-40%

Lmk61pd0a2 Oscillator Module 100MHz PLL low Noise Differential Reference

$ 34.74

- Description

- Size Guide

Description

Lmk61pd0a2 Oscillator Module 100MHz PLL low Noise Differential Reference1、 Index parameters

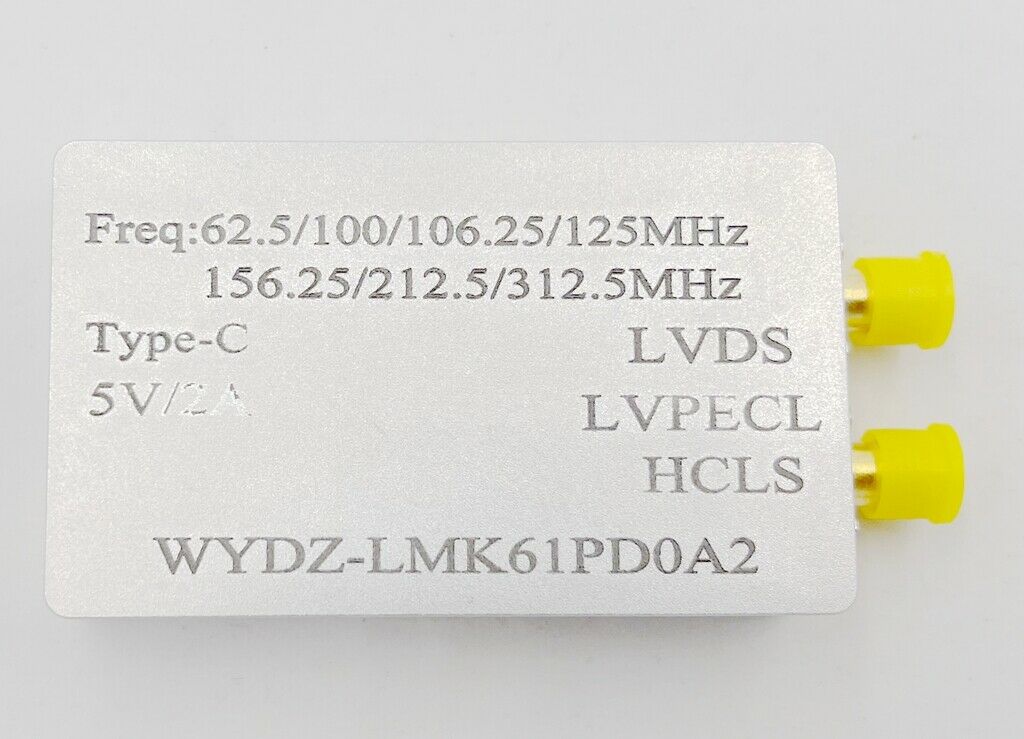

1. Output frequency: 62.5m-100m-106.25m-125m-156.25m-212.5m-312.5m

2. Differential output mode: LVPECL, LVDS, HCSL

3. Power supply: type-C (+ 5V)

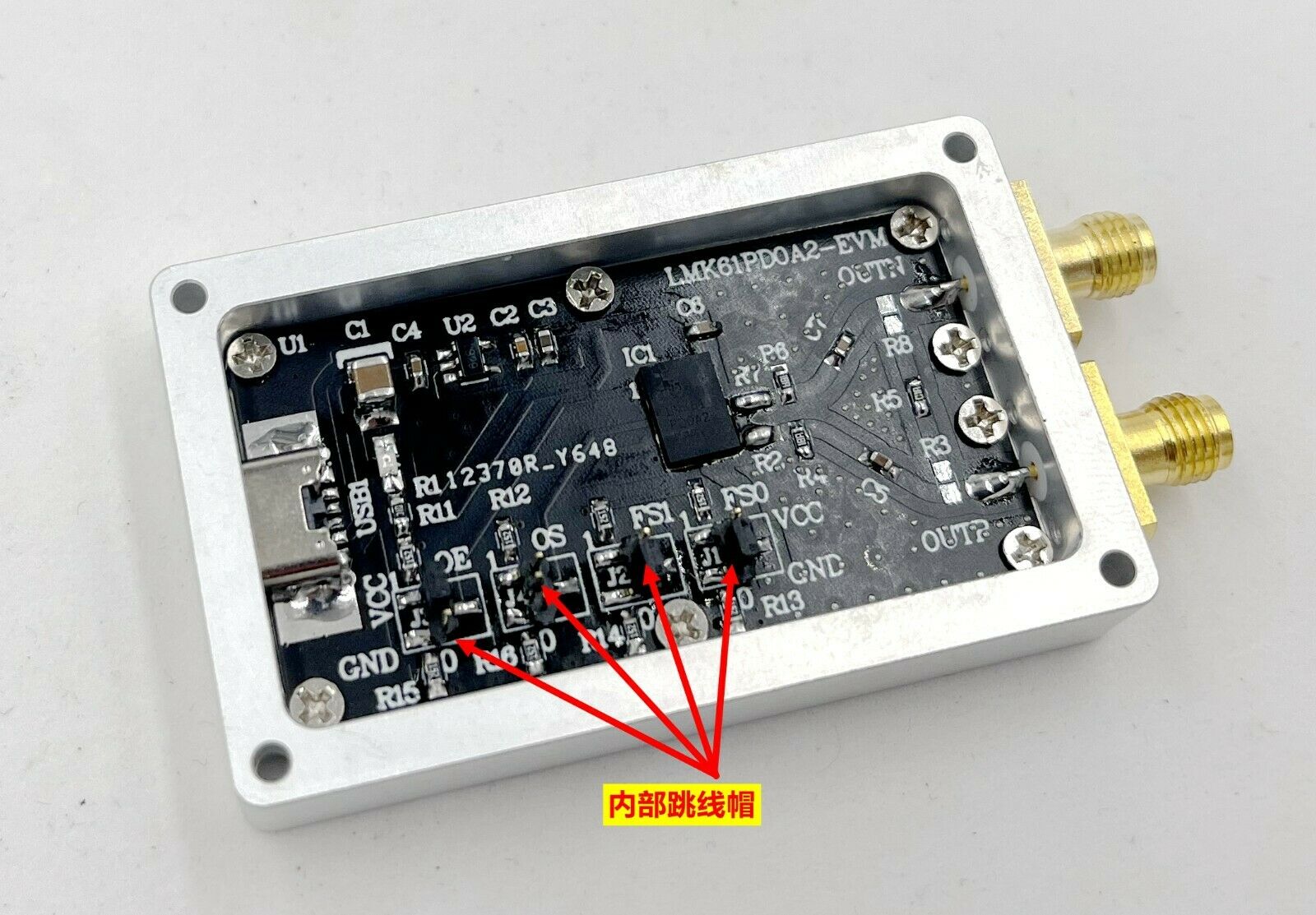

4. Control mode: internal jumper cap configuration output frequency and differential output mode

5. Delivery: one host (including fully shielded aluminum alloy shell) + type-C cable

6. The default jumper cap configuration is: 100MHz, LVPECL output

7. Module size: 60 * 36 * 14mm

8. Output interface type: SMA (outer screw inner hole)

2、 Difference of three different driving modes

The supported signal types are LVPECL (low voltage positive emitter coupling) logic, LVDS (low voltage differential signal), HCSL (current guidance logic of highspeed)

LVPECL is low voltage positive emitter couple logic, which uses 3.3V or 2.5V power supply. To understand the LVPECL circuit, we should first recognize the PECL circuit. PECL, or positive emitter couple logic, uses a 5.0V power supply. PECL is evolved from ECL, which is emitter couple logic. The circuit is an unsaturated digital logic circuit. The transistors in the circuit work in the linear region or cut-off region, and the speed is not limited by the storage time of minority carriers. Therefore, it is the fastest of all kinds of existing logic circuits, and can meet the working speed of up to 10Gbps. ECL has two supply voltages VCC and Vee. When Vee is grounded and VCC is connected to positive voltage, the logic is called PECL; When VCC is grounded and Vee is connected to negative voltage, the logic becomes necl, and Vee is generally connected to - 5.2v power supply; ECL in a narrow sense refers to necl. Because PECL / LVPECL can share a positive power supply with other circuits in the system, PECL / LVPECL is more widely used than ECL. At first, PECL devices connected VCC to + 5V. Later, LVPECL (low voltage PECL) with VCC = 3.3v/2.5v appeared in order to directly use the widely used voltage of 3.3V and 2.5V.

LVDS (low voltage differential signaling) is a low swing differential signal technology, which enables the signal to be transmitted at the rate of several hundred Mbps on the differential PCB pair or balanced cable. Its low amplitude and low current drive output realize low noise and low power consumption. LVDS (low voltage differential signaling) is a small amplitude differential signal technology. LVDS signal transmission generally consists of three parts: differential signal transmitter, differential signal interconnector and differential signal receiver.

Each HCSL output pin of HCSL switches between 0 and 14mA. When one output pin is low level (0), the other is high level (driving 14mA). The equivalent load resistance of HCSL driver is 68 Ω, which is 28.81 Ω in parallel with 50 Ω resistor. The CML input swing is 14max28.81 Ω = 403mv. A 10nf AC coupling capacitor should be placed in front of the CML receiver to block the DC level from the HCSL driver. In addition, the self bias inside the CML receiver input must be confirmed. If there is no CML input self bias, a 50 Ω termination resistor must be placed on the PCB with CML bias and transmission line termination to the VCC.

3、 Control mode + internal chart

4、 Reserved hardware interface

五、实测波形

1

、62.5M

2

、100M

3

、106.25M

4

、125M

5

、156.25M

6

、212.5M

7

、312.5M

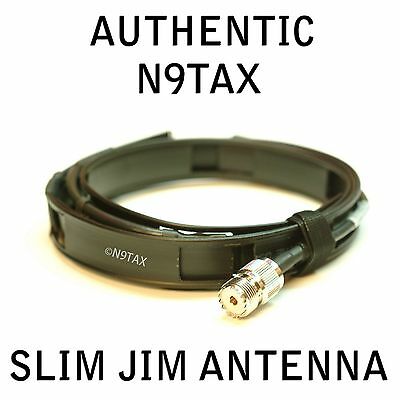

6、 Physical picture